## PATENT ABSTRACTS OF JAPAN

(11)Publication number : 09=017890

(43)Date of publication of application : 17.01.1997

| (51)Int.CI.                        |            | H01L 21/8247<br>H01L 29/788<br>H01L 29/792<br>H01L 27/115 |                       | ······································ |

|------------------------------------|------------|-----------------------------------------------------------|-----------------------|----------------------------------------|

| (21)Application number : 07-160486 |            | (71)Applicant : TOSHIBA                                   | ······                |                                        |

| (22)Date of filing :               | 27.06.1995 | (72)Inventor : SONODA<br>TSUNOD                           | MASAHISA<br>A HIROAKI |                                        |

(54) MANUFACTURE OF NONVOLATILE SEMICONDUCTOR MEMORY DEVICE

## (57)Abstract:

PURPOSE: To avoid causing the overerase in flash EEPROM.

CONSTITUTION: On the surface of a semiconductor substrate 1 a tunnel insulation film 4, floating gate electrode material, insulation film and control gate electrode material are deposited and patterned to form a floating gate electrodes 5 and control gate electrodes 6, then the floating electrode material is isotropically etched by giving priority to it through a specifically patterned resist used as a mask to increase the radius of curvature of the corner of the electrode 5 at the side of the source region 2. The resist is then removed, it is heat treated in an atmosphere of 0, the electrodes 5 are covered with an insulation film 8, the corners of these electrodes 5 are cut to increase their radius of curvature over 10nm, thereby forming source regions 2 and drain regions 3. Thus, the controllability of the amount of electrons in the electrode 5 can be improved. and

hence the overerase can be avoided and memory hold characteristic can be improved.

## LEGAL STATUS

[Date of request for examination] 17

[Date of sending the examiner's decision of rejection]

[Kind of final disposal of application other than the examiner's decision of rejection or application converted registration]

[Date of final disposal for application]

[Patent number]

[Date of registration]

[Number of appeal against examiner's decision of rejection]

17.03.2000

(12) 公開特許公報(A)

(11)特許出願公開番号

## 特開平9-17890

(43)公開日 平成9年(1997)1月17日

| (51) Int.Cl. <sup>6</sup> |         | 識別記号 | 庁内整理番号 | FI   |       |     | 技術表示箇所 |

|---------------------------|---------|------|--------|------|-------|-----|--------|

| HOIL                      | 21/8247 |      | · .    | HOIL | 29/78 | 371 |        |

|                           | 29/788  |      |        |      | 27/10 | 434 |        |

|                           | 29/792  |      |        |      |       |     |        |

|                           | 27/115  |      |        |      |       |     |        |

|                           |         |      |        |      |       |     |        |

審査請求 未請求 請求項の数8 OL (全 12 頁)

| 特顯平7-160486     | (71)出顧人 000003078   |                                                                                                                                                                      |

|-----------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | 株式会社東芝              |                                                                                                                                                                      |

| 平成7年(1995)6月27日 | 神奈川県川崎市幸区堀川町72番地    |                                                                                                                                                                      |

|                 | (72)発明者 園田 真久       |                                                                                                                                                                      |

|                 | 神奈川県川崎市幸区小向東芝町1番地   | 株                                                                                                                                                                    |

|                 | 式会社東芝多摩川工場内         |                                                                                                                                                                      |

|                 | (72)発明者 角田 弘昭       |                                                                                                                                                                      |

|                 | 神奈川県川崎市幸区小向東芝町1番地   | 株                                                                                                                                                                    |

|                 | 式会社東芝多摩川工場内         |                                                                                                                                                                      |

|                 | (74)代理人 弁理士 大胡 典夫   |                                                                                                                                                                      |

|                 | (14)11,理入 升型工 大樹 典大 |                                                                                                                                                                      |

|                 |                     | 平成7年(1995)6月27日       株式会社東芝<br>神奈川県川崎市幸区堀川町72番地         (72)発明者 園田 真久<br>神奈川県川崎市幸区小向東芝町1番地<br>式会社東芝多摩川工場内         (72)発明者 角田 弘昭<br>神奈川県川崎市幸区小向東芝町1番地<br>式会社東芝多摩川工場内 |

(54) 【発明の名称】 不揮発性半導体記憶装置の製造方法

(57)【要約】

【目的】 フラッシュEEPROMにおいて、過消去の発生を 防止すること。

【構成】 半導体基板1 表面に順にトンネル絶縁膜4、 浮遊ゲート電極材料、絶縁膜、制御ゲート電極材料を堆 積し、これらトンネル絶縁膜4、浮遊ゲート電極材料、 絶縁膜、制御ゲート電極材料をパターニングし浮遊ゲー ト電極5 及び制御ゲート電極6 を形成した後、所定パタ ーニングしたレジストをマスクに浮遊ゲート電極材料を 優先的に等方性エッチングし、浮遊ゲート電極5 のソー ス領域2 側の角の曲率半径を大きくする。そして、レジ ストを除去して酸素雰囲気で熱処理を行い、浮遊ゲート 電極5 を絶縁膜8 で覆うと共に、浮遊ゲート電極5 の角 の曲率半径を10mm以上に加工し、ソース領域2 及びドレ イン領域3 を形成する。これより、浮遊ゲート電極5 中 の電子の量の制御性を向上できるため、過消去を防止で き、且つ記憶保持特性を向上できる。

【特許請求の範囲】

【請求項1】 半導体基板上にトンネル絶縁膜、浮遊ゲート電極形成材料、絶縁膜、制御ゲート電極形成材料を 順次形成する工程と、

所定パターニングしたレジストをマスクに前記制御ゲー ト電極形成材料、絶縁膜、及び浮遊ゲート電極形成材料 を異方性エッチングすることより、浮遊ゲート電極及び 制御ゲート電極を形成した後、このレジストを除去する 工程と、

前記浮遊ゲート電極及び前記制御ゲート電極の1つの側 面が露出するよう前記浮遊ゲート電極の上にレジストを 形成する工程と、

このレジストをマスクに前記浮遊ゲート電極の露出した 側面を等方性エッチングし、前記浮遊ゲート電極の端部 のうち前記トンネル絶縁膜と接するコーナー部分の曲率 半径を大きくする工程と、

等方性エッチング後、前記レジストを除去する工程と、 レジスト除去後、熱処理を行い前記浮遊ゲート電極のコ ーナー部分の曲率半径を10nm以上にする工程と、

前記制御ゲート電極下の前記半導体基板にチャネル領域 を規定するように、曲率半径が10mm以上の前記浮遊ゲー ト電極のコーナー部分側に第一の不純物領域を、前記コ ーナー部分と反対に位置する前記浮遊ゲート電極のトン ネル絶縁膜と接する端部側に第二の不純物領域を形成す る工程とを有することを特徴とする不揮発性半導体記憶 装置の製造方法。

【請求項2】 上記浮遊ゲート電極と第一の不純物領域 との重なり部分は、この浮遊ゲート電極と第二の不純物 領域との重なり部分より大きいことを特徴とする請求項 1記載の不揮発性半導体記憶装置の製造方法。

【請求項3】 半導体基板上にトンネル絶縁膜、浮遊 ゲート電極形成材料、絶縁膜、制御ゲート電極形成材料 を順次形成する工程と、

所定パターニングしたレジストをマスクに前記浮遊ゲート電極形成材料、絶縁膜、及び制御ゲート電極形成材料 を異方性エッチングすることより、浮遊ゲート電極及び 制御ゲート電極を形成する工程と、

浮遊ゲート電極を形成した後、前記レジストをマスク に、前記浮遊ゲート電極の露出した両側面を等方性エッ チングし、前記トンネル絶縁膜と接する2つのコーナー 部分の曲率半径を大きくする工程と、

等方性エッチング後、前記レジストを除去する工程と、 レジスト除去後、熱処理を行い前記浮遊ゲート電極の2 つのコーナ部分の曲率半径を10nm以上にする工程と、

前記制御ゲート電極下の前記半導体基板にチャネル領域 を規定するように第一の不純物領域及び第二の不純物領 域を形成する工程とを有することを特徴とする不揮発性 半導体記憶装置の製造方法。

【請求項4】 上記浮遊ゲート電極形成材料に不純物を ドープした多結晶Siを使用し、且つ上記熱処理は酸素雰 【請求項5】 上記浮遊ゲート電極形成材料に不純物を ドープした多結晶Siを使用し、且つ上記熱処理は酸素雰 囲気で行なうことにより浮遊ゲート電極の周辺部を酸化 させ、その後堆積した層間絶縁膜を平坦化する処理であ ることを特徴とする請求項1又は請求項3記載の不揮発 性半導体記憶装置の製造方法。

【請求項6】 上記等方性エッチングは、CF4 ガスと02 ガスとの混合ガスを用いることを特徴とする請求項4 記載の不揮発性半導体記憶装置の製造方法。

【請求項7】 上記浮遊ゲート電極の端部のうちトンネ ル絶縁膜と接するコーナー部分の曲率半径が50mm以上で あることを特徴とする請求項1又は請求項3記載の不揮 発性半導体記憶装置の製造方法。

【請求項8】 上記チャネル領域は、N型領域であり、 且つ第一の不純物領域はソース領域であり、且つ第二の 不純物領域はドレイン領域であることを特徴とする請求 項1又は請求項3記載の不揮発性半導体記憶装置の製造 方法。

【発明の詳細な説明】

[0001]

【産業上の利用分野】本発明は、電気的に書き込み及び 消去を行なうことが可能な不揮発性半導体記憶装置(EEP ROM ; Erasable and Electrically Programmable Read Only Memory)に関する。

[0002]

【従来の技術】EEPROMは、(1) 電源供給を断った場合に も、デバイスの記憶情報が消滅しない(不揮発性)、(2) 電気的に消去及び書き込みが可能という特徴を有して いる。このため、ファクシミリのインターフェース設定 や短縮ダイアルの登録を始め、システムに組み込んだ後 に変更があるデータの保存に使用される等、その用途範 囲は広い。

【0003】それに加え16M から64M、256Mと大容量化 が見え始めた今日においては、携帯情報端末・サブノー トパソコン向けのファイル用メモリーとして開発に拍車 がかかっている。

【0004】以下、EEPROMの代表的な構造を、ETOX(EPR OM Thin Oxide)型フラッシュEEPROMを例に説明する。

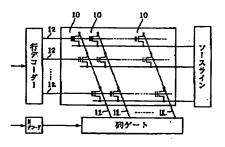

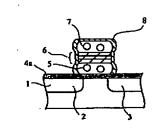

【0005】一般にメモリは、1ビットの情報を記憶す る単位回路であるメモリセルより構成されている。図10 のメモリのブロック図のように、各メモリセル10には、 入力データ及び出力データを転送するビット線11と、ビ ット線11とメモリセル10を接続するワード線12が接続さ れ、行デコーダで一本のワード線12を選択した後、その ワード線12上のメモリセル10にビット線11を介して書き 込みを行なったり、メモリセル10の情報をビット線11を 介しセンスアンプ13で増幅し出力バッファ14に転送し読 み出しを行なっている。

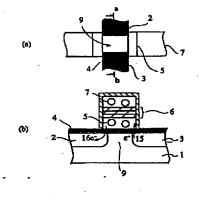

【0006】具体的には、NOR 型接続の ETOX 型フラッシュEEPROMのメモリセルアレイは図11のようになり、一 つのメモリセル10を上からみた平面図は図12(a) のよう になる。この図12(a) のa - b線に沿って見た断面図 が、図12(b) に示すような、浮遊ゲートと制御ゲートの

2つのゲート構造を有するMOSFET(Metal Oxide Semicon ductor Field Effect Transistor) である。

【0007】この例では、P型半導体基板1 にN<sup>+</sup>型の ソース領域2 及びドレイン領域3 が形成され、ソース領 域2 とドレイン領域3 の間に形成されるチャネル領域9 上には、トンネル絶縁膜4 を介して浮遊ゲート電極5 が 形成されている。浮遊ゲート電極5 上には、下層から順 にSi酸化膜/Si窒化膜/Si酸化膜の複合膜 (0N0 膜6)

を介して、制御電極7 が形成されている。そして、浮遊 ゲート電極5 、0N0 膜6 、及び制御ゲート電極7 の周囲 には、後酸化膜(熱酸化膜)8が形成されている。

【0008】図13(a) 乃至(c) は、上述した従来の不揮 発性半導体記憶装置の製造工程を示した断面図である。 【0009】この従来の不揮発性半導体記憶装置の製造

方法は、以下のとおりである。

【0010】(1) 半導体基板1 表面に、トンネル絶緑膜 4 としてSi酸化膜4aを形成した後、不純物をドープした 多結晶Si膜5aを形成する。そして、多結晶Si膜5a上に、 順にSi酸化膜/Si窒化膜/Si酸化膜を堆積して0N0 膜6 を形成した後、不純物をドープした多結晶Si膜7aを形成 する(図13(a)図示)。

【0011】(2) 所定パターニングを行なったレジスト 18をマスクに、多結晶Si膜5a、ONO膜6、多結晶Si膜7a を異方性エッチングして、浮遊ゲート電極5及び制御ゲ ート電極7を形成し(図13(b)図示)、レジスト18を除 去する。

【0012】(3) レジスト18を 02 プラズマ処理と硫酸 と過酸化水素の混合液で除去し、酸素雰囲気で熱処理し 後酸化膜8 を形成した後、制御ゲート電極7 を覆うレジ スト18をマスクに不純物を注入してソース領域2 及びド レイン領域3 を形成し、レジスト18を除去する(図13 (c)図示)。

【0013】ここで、ソース領域2及びドレイン領域3 を含む浮遊ゲート電極の断面における4つの角は、約90 。(曲率半径=0)であり、(3)の熱処理により多少丸 くなったとしても、その曲率半径は10nm以下である。 【0014】このようなメモリにおいて、データを書き

込むには、浮遊ゲート電極5 へ電子を注入15し、消去 は、浮遊ゲート電極5 からの電子の引き抜き16によって 行なう。また、読み出しは、浮遊ゲート電極5 中の電子 数の増減により、制御ゲート電極7 からみたしきい値が 増減することを利用し、選択メモリセルの所定部に所定 電圧を印加した際、電流が流れるか否かで、'1' か'0' かを認識する。 【0015】従って、浮遊ゲート電極5 中に存在する電子の量を正確に制御することが、このメモリの記憶情報の正確さにつながっている。

[0016]

【発明が解決しようとする課題】ETOX型フラッシュEEPR OMにおいては、特定のメモリセルを指定して消去を行な わず、インテリジェント方式等により、一括消去を行な っている。

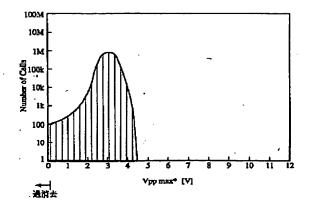

【0017】図13は、ワード線からみたメモリセルのし きい値電圧と、そのしきい値電圧を有するメモリセルの 数の関係を表した図である。

【0018】図13より、各メモリセルにおけるしきい値 電圧のばらつきが大きく、同一条件による一括消去の難 しいことがわかる。

【0019】また、この点から推測されるが、インテリ ジェント方式は全メモリセルの消去を確認するまで消去 動作を繰り返し行なうため、浮遊ゲート電極から電子を 引き抜きすぎたメモリセル、すなわち、図13のように、 しきい値電圧がOV以下となる過消去が存在していた。こ の過消去は、NOR型接続においては、制御ゲート電極が 非選択状態(OV)であっても電流が流れるため、同一ビ ット線上のメモリセルデータが読めなくなる問題となっ ていた。

【0020】加えて、NOR 型接続においては、選択メモ リセルと同じワード線上にある非選択メモリセルに、書 き込み時に高電圧が加わる、或は読み出し時に低電圧が 長時間加わるため、非選択メモリセルの浮遊ゲート電極 に電子が入り、記憶状態が不正確になる問題を有してい た。

【0021】このため、本発明は、一括消去時の消去動 作の回数を低減させ、過消去の発生を防止し、また、書 き込み及び読み出し時に生じる記憶保持特性の低下を抑 制することを目的とする。

[0022]

【課題を解決するための手段】上記目的を達成するため に、本発明の不揮発性半導体記憶装置は、半導体基板上 にトンネル絶縁膜、浮遊ゲート電極形成材料、絶縁膜、 制御ゲート電極形成材料を順次形成する工程と、所定パ ターニングしたレジストをマスクに前記制御ゲート電極 形成材料、絶縁膜、及び浮遊ゲート電極形成材料を異方 性エッチングすることより、浮遊ゲート電極及び制御ゲ ート電極を形成した後、このレジストを除去する工程 と、前記浮遊ゲート電極及び前記制御ゲート電極の1つ の側面が露出するよう前記浮遊ゲート電極の上にレジス トを形成する工程と、このレジストをマスクに前記浮遊 ゲート電極の露出した側面を等方性エッチングし、前記 浮遊ゲート電極の端部のうち前記トンネル絶縁膜と接す るコーナー部分の曲率半径を大きくする工程と、等方性 エッチング後、前記レジストを除去する工程と、レジス ト除去後、熱処理を行い前記浮遊ゲート電極のコーナー

部分の曲率半径を10nm以上にする工程と、前記制御ゲート電極下の前記半導体基板にチャネル領域を規定するように、曲率半径が10nm以上の前記浮遊ゲート電極のコーナー部分側に第一の不純物領域を、前記コーナー部分と反対に位置する前記浮遊ゲート電極のトンネル絶縁膜と接する端部側に第二の不純物領域を形成する工程とを有することを特徴とする。

【0023】尚、上記浮遊ゲート電極と第一の不純物領 域との重なり部分は、この浮遊ゲート電極と第二の不純 物領域との重なり部分より大きいことを特徴とする。

【0024】又、上記目的を達成するために、本発明の 不揮発性半導体記憶装置は、半導体基板上にトンネル絶 縁膜、浮遊ゲート電極形成材料、絶縁膜、制御ゲート電 極形成材料を順次形成する工程と、所定パターニングし たレジストをマスクに前記浮遊ゲート電極形成材料、絶 縁膜、及び制御ゲート電極形成材料を異方性エッチング することより、浮遊ゲート電極及び制御ゲート電極を形 成する工程と、浮遊ゲート電極を形成した後、前記レジ ストをマスクに、前記浮遊ゲート電極の露出した両側面 を等方性エッチングし、前記トンネル絶縁膜と接する2 つのコーナー部分の曲率半径を大きくする工程と、等方 性エッチング後、前記レジストを除去する工程と、レジ スト除去後、熱処理を行い前記浮遊ゲート電極の2つの コーナ部分の曲率半径を10nm以上にする工程と、前記制 御ゲート電極下の前記半導体基板にチャネル領域を規定 するように第一の不純物領域及び第二の不純物領域を形 成する工程とを有することを特徴とする。

【0025】尚、上記浮遊ゲート電極形成材料に不純物 をドープした多結晶Siを使用し、且つ上記熱処理は酸素 雰囲気で行なうことにより浮遊ゲート電極の周辺部を酸 化させる処理であることを特徴とする。

【0026】尚、上記浮遊ゲート電極形成材料に不純物 をドープした多結晶Siを使用し、且つ上記熱処理は酸素 雰囲気で行なうことにより浮遊ゲート電極の周辺部を酸 化させ、その後堆積した層間絶縁膜を平坦化する処理で あることを特徴とする。

【0027】尚、上記等方性エッチングは、CF4 ガスと 02 ガスとの混合ガスを用いることを特徴とする。

【0028】尚、上記浮遊ゲート電極の端部のうちトン ネル絶縁膜と接するコーナー部分の曲率半径が50nm以上 であることを特徴とする。

【0029】尚、上記チャネル領域は、N型領域であ り、且つ第一の不純物領域はソース領域であり、且つ第 二の不純物領域はドレイン領域であることを特徴とす る。

[0030]

【作用】ソース領域-ドレイン領域に沿った方向に対 し、浮遊ゲート電極のトンネル絶縁膜と接するソース領 域及びドレイン領域側の角(便宜上、浮遊ゲート電極の 角と称す)の曲率半径が10nm以上になっている。立体的 にみると、この断面形状が、ソース領域-ドレイン領域 に沿った方向に対し垂直な方向に、浮遊ゲート電極の所 定の長さにおいて続いている。

【0031】これによれば、浮遊ゲート電極に電圧を印 加した時、浮遊ゲート電極の角部分に加わる電界は、従 来に比べて小さくなる。

【0032】このため、書き込み及び読み出し時に選択 メモリセルのゲート電極に電圧を印加した際、選択メモ リセルと同じワード線上にある非選択メモリセルにおい て、ソース領域及びドレイン領域から浮遊ゲート電極 へ、電子が注入することを避けられる。

【0033】また、以下に示すような作用も得られる。 【0034】トンネル絶縁膜による電気容量を COX、浮 遊ゲート電極と制御電極間の絶縁膜による電気容量を C ONO、浮遊ゲート電極に電圧を印加した場合に生じる浮 遊ゲート電極にかかる電圧を VFG、制御ゲート電極にか かる電圧を VCCとおく。

$[0 0 3 5] C_{OX} \cdot V_{FG} = C_{ONO} (V_{CG} - V_{FG}) \pm 0$

$V_{FG} = C_{ONO} (C_{ONO} + C_{OX}) - 1 \cdot V_{CG}$

(ここに  $C_{ONO}$  ( $C_{ONO}$  +  $C_{OX}$ )  $-\tilde{1}$ はカップリング比と 定義される)となる。

【0036】本発明では、浮遊ゲート電極の角の曲率半 径が大きくなったことから、複数のメモリセルにおい て、浮遊ゲート電極への電子の出入りの際、電子が通過 する領域にあるトンネル絶緑膜(電気容量を決定するト ンネル絶緑膜)のサイズのばらつきが減少する。特に、 ソース領域側の浮遊ゲート電極の角の曲率半径が大きく なったことは、トンネル絶緑膜のサイズのばらつき減少 に寄与している。なぜなら、ソース領域おける浮遊ゲー ト電極との重なりは、ドレイン領域における重なりより 大きいためである。

【0037】これにより、 COXが均一になるため、カッ プリング比のばらつきが減少し、制御ゲート電極に印加 する電圧が同じ場合、浮遊ゲート電極に加わる電圧、つ まり電界は均一になる。

【0038】よって、一括消去を行いやすくなり過消去 の発生を防止できる。

【0039】

【実施例】以下、図面を参照して本発明の不揮発性半導 体記憶装置を説明する。

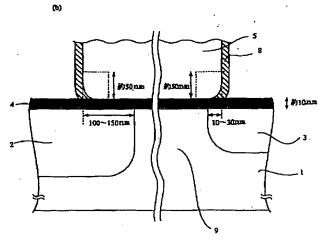

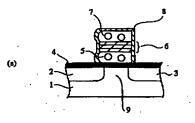

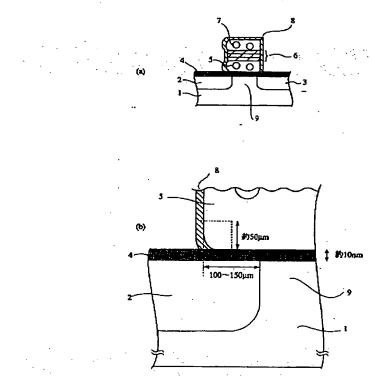

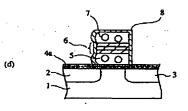

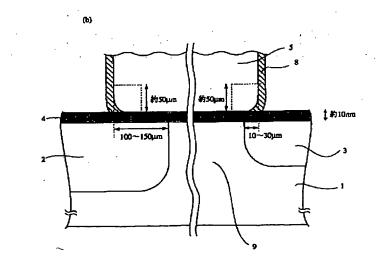

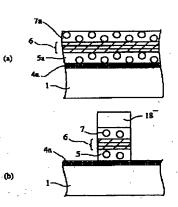

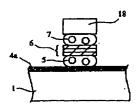

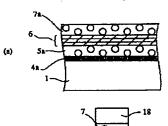

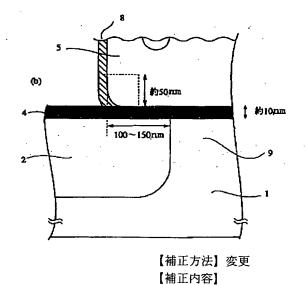

【0040】図1(a)及び(b)は、各々本発明の第一の実施例の不揮発性半導体記憶装置を図12のa -b線に沿った線からみた概略断面図、その拡大図である。また図2 (a)乃至(d)は、本発明の第一の実施例の不揮発性半導体記憶装置の製造工程を示した概略断面図である。

【0041】図1(a)のように、P型半導体基板1 にN + 型のソース領域2及びドレイン領域3 が、ソース領域2 とドレイン領域3 の間に形成されるチャネル領域9 上に はトンネル絶縁膜4 を介して、浮遊ゲート電極5 が形成 されている。浮遊ゲート電極5 上には、下層から順にSi 酸化膜、Si窒化膜、Si酸化膜からなるONO 膜6 を介し て、制御電極7 が形成されている。そして、浮遊ゲート 電極5 、ONO 膜6 、及び制御ゲート電極7 の周囲には、 後酸化膜(Si 酸化膜)8が形成されている。

【0042】第一の実施例では、図1(b)のように、浮遊 ゲート電極5の下面におけるソース領域2 側の曲率半径 は約50nmになっている。また、トンネル絶縁膜の膜厚及 び後酸化膜厚は約10nm、浮遊ゲート電極5 とソース領域 2 の重なりは約100~150nm、ドレイン領域3 との重な りは約10~30nmとなっている。

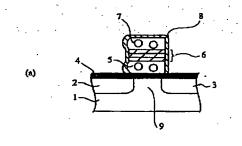

【0043】次に、本実施例の不揮発性半導体記憶装置 の製造方法を述べる。

【0044】(1) 半導体基板1 表面に、トンネル絶緑膜 4 としてSi酸化膜4aを形成した後、不純物をドープした 多結晶Si膜5aを形成する。そして、多結晶Si膜5a上に、 順にSi酸化膜/Si窒化膜/Si酸化膜を堆積して0N0 膜6 を形成した後、不純物をドープした多結晶Si膜7aを形成 する(図2(a)図示)。

【0045】(2)所定パターニングを行なったレジスト 18をマスクに、多結晶Si膜5a、0N0膜6、多結晶Si膜7a を異方性エッチングして、浮遊ゲート電極5及び制御ゲ ート電極7を形成し、レジスト18を除去する(図2(b)図 示)。

【0046】(3) ソース領域2 予定側の浮遊ゲート電極 5 0N0 膜6 ・制御ゲート電極7 の側面、及びこの側面 の上側の制御ゲート電極7 の角以外を覆うレジスト18を パターニングし(図2(c)図示)、多結晶Si膜5a,7a を選 択的に除去するエッチングガス、例えばCF4 と 02 の混 合ガスを用いて等方性エッチングを行なう。

【0047】(4) レジスト18を 02 プラズマ処理と硫酸 と過酸化水素の混合液で除去し、酸素雰囲気で熱処理し 後酸化膜8 を形成した後、制御ゲート電極7 を覆うレジ スト18をマスクに不純物を注入してソース領域2 及びド レイン領域3 を形成し、レジスト18を除去する(図2(d) 図示)。この後、図示せぬが、層間絶縁膜を形成し平坦 化のため熱処理を行なった後、コンタクトホールの開 孔、配線を形成することにより、不揮発性半導体装置が 形成される。

【0048】(3)の等方性エッチングにおいて、エッチ ングガス、例えばCF4 と02 の混合ガスは、多結晶Si膜 5a,7a とONO 膜6 との界面、多結晶Si膜5aとトンネル絶 縁膜4 との界面に入り易い。そのため、多結晶Si膜5a,7 a において界面部分は、他の部分よりエッチングが進 み、浮遊ゲート電極5 のトンネル絶縁膜4 と接する角の 曲率半径が大きくなる。さらに、(4)の後酸化膜8 の形 成時の熱処理により、若しくは後酸化膜8 の形成時の熱 処理及び層間絶縁膜の平坦化のために行なう熱処理によ り、浮遊ゲート電極5 の周辺部が酸化するため、ソース

領域側2の浮遊ゲート電極5のトンネル絶縁膜4と接す る角がに丸みを生じることができ、最終的に曲率半径を 50nmにすることができる。

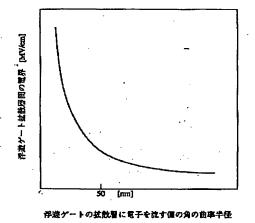

【0049】図3は、浮遊ゲート電極から引き抜いた電 子を受ける不純物領域(本実施例ではソース領域2)側に おける浮遊ゲート電極の角の曲率半径と浮遊ゲート電極 5 ソース領域3間の電界の関係を表した図である。こ の図より、次の2つの傾向を読み取ることができる。

【0050】(傾向1) 曲率半径が浮遊ゲート電極5 の エッジの曲率半径が大きくなると、そのエッジにおける 電界は小さくなる。

【0051】(傾向2) 全メモリセルをみた場合、同じ 製造工程を経ていながら、必ず浮遊ゲート電極5の角の 曲率半径にはばらつきがあった。曲率半径の全体の平均 値に対するばらつきΔrによる電界のばらつきをΔEと おくと、曲率半径が大きい程、ΔEは小さくなる。

【0052】以下、この2つの傾向より得られる2つの 効果について述べる。

【0053】第一に、本実施例のメモリセルをNOR 型接 続したメモリにおいて、書き込み・読み出しを行なった 場合を考える。

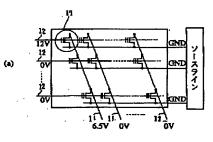

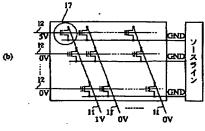

【0054】書き込みを行なう場合には、図4(a)のよう に、選択メモリセル17の存在するワード線11に12V、ビ ット線12に6.5V、その他のワード線12、及びビット線11 に0Vを印加する。

【0055】このため、選択メモリセル17と同一ワード 線11に存在する非選択メモリセルの制御ゲート電極7 に も高電圧が印加されるが、本実施例では傾向1 より、ソ ース領域2 側の浮遊ゲート電極5 の角にかかる電界が小 さくなっているため、浮遊ゲート電極5 に電子が入る誤 書き込みを抑制できる。

【0056】読み出しを行なう場合には、図4(b)のよう に、選択メモリセル17の存在するワード線11に5V、ビッ ト線12に1V、その他のワード線12及びビット線11に0Vを 印加する。

【0057】書き込み時と比較して低電圧ではあるが、 読み出しに時間がかかかるため、選択メモリセル17と同 ーワード線11に存在する非選択メモリセルの制御ゲート 電極7に5Vが長時間加わる。しかし、本実施例では傾向 1より、ソース領域2側の浮遊ゲート電極5の角にかか る電界が小さくなっているため、浮遊ゲート電極5に電 子が入る誤書き込みを抑制できる。

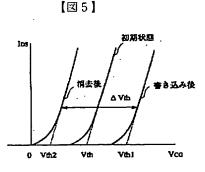

【0058】周知のとおり、図5のように、浮遊ゲート 電極に電子の注入または引き抜きを行なっていない初期 状態に比べ、書き込み後のソース・ドレイン間の電流 I DSとゲート電極にかかる電圧 VCC関係を表す特性は、従 来に比べ右にシフトし、しきい値電圧Vth は上昇しVth1 となる。また、消去後の IDSと VCC関係を表す特性は、 左にシフトし、しきい値電圧は低下しVth2となる。

【0059】本実施例では、書き込み時または読み出し 時の誤書き込みを抑制できるため、Vth1とVth2の差ΔVt h を保持することができる。

特開平9-17890

【0060】すなわち、記憶状態を長期間、正確に維持 できる。従って、従来より、記憶特性の向上が図れる。 【0061】第二に、16ビット×L×10<sup>M</sup> ワード (L=2 <sup>N</sup>/16;N,M 自然数)構成のメモリセルにおいて一括消 去を行なう場合を考える。

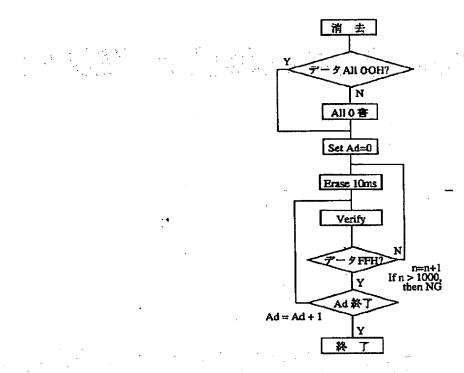

【0062】消去においては、図6 にフローチャートを 示したように、インテリジェント・イレーズ方式を採用 した。

【0063】最初に各ワード線上の16メモリセルをチェ ックし、書き込み状態でないメモリセルに書き込みを行 い、全メモリセルの書き込みを確認後、選択メモリセル のアドレスを0から順にL×10<sup>M</sup>-1まで指定し、各々 について次の工程を行なう。同一ワード線上の16のメモ リセルの所定部に所定電圧を10m秒与え、浮遊ゲート電 極中の電子を引き抜く消去動作を行なった後、1つのメ モリセルを読み出し、それが消去状態になるまで、消去 動作・読み出しを交互に行なう(この一連の作業を、サ イクル工程と呼ぶ)。そして、16のメモリセルの消去を 確認するまで、メモリセルを一つずつチェックし、未消 去のメモリセルを発見した場合にはサイクル工程を行 う。

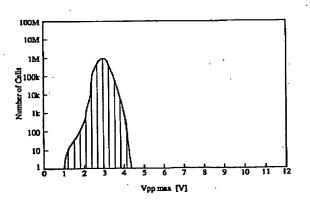

【0064】図7は、一括消去の結果について、ワード 線からみたメモリセルのしきい値電圧と、そのしきい値 電圧を有するメモリセルの数の関係を表した図である。

【0065】この図より、しきい値電圧のばらつきは従 来に比べ減少し、さらにしきい値電圧が0V以下の過消去 が存在しないことがわかる。

【0066】理由は、一連の消去動作において本実施例 のメモリセルは、傾向1より、浮遊ゲート電極5の角に 高電界が働かないため、浮遊ゲート電極5からの過度の 電子の引き抜きを抑止できるからである。

【0067】また、傾向2より、各メモリセルにおい て、メモリセルに電圧を印加した際生じる各メモリセル の電界のばらつきが減少したため、各メモリセルの浮遊 ゲート電極5中の電子の量を同一条件で同様に制御でき るからである。

【0068】以上より、 ETOX 型フラッシュEEPROMにお いては、少ない消去動作回数で一括消去を行なえ、過消 去防止の効果を得られる。

【0069】従って本実施例によれば、過消去を防止で き、且つ、記憶保持特性を向上できる。

【0070】次に、第一の実施例の応用例を述べる。

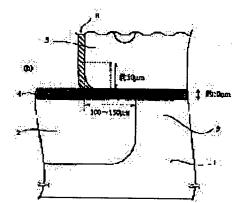

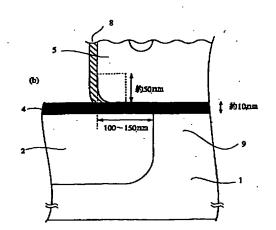

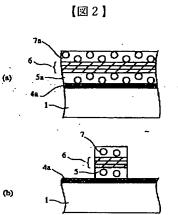

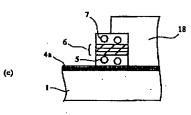

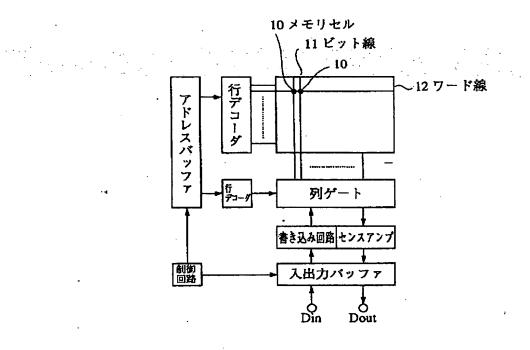

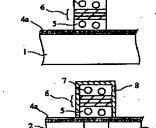

【0071】図8(a)及び(b) は、各々本発明の第一の実 施例の応用例にかかる不揮発性半導体記憶装置を図12の a -b 線に沿った線からみた概略断面図、その拡大図で ある。また図9(a)乃至(d) は、本発明の第一の実施例の 不揮発性半導体記憶装置の製造工程を示した概略断面図 である。

【0072】図8(a)及び(b)のように、この不揮発性半 導体記憶装置は、浮遊ゲート電極5の下面におけるソー ス領域2 側及びドレイン領域3 側の両サイドにあるエッジの曲率半径が、50nmになっている。また、トンネル絶 緑膜4 の膜厚及び後酸化膜8厚は約10nm、浮遊ゲート電 極5 とソース領域2 の重なりは約100 ~150nm 、ドレイ ン領域3 との重なりは約10~30nmとなっている。

【0073】本実施例の不揮発性半導体記憶装置の製造 方法は、次のとおりである。

【0074】(1) 半導体基板1 表面に、トンネル絶緑膜 4 としてSi酸化膜4aを形成した後、不純物をドープした 多結晶Si膜5aを形成する。そして、多結晶Si膜5a上に、 順にSi酸化膜/Si窒化膜/Si酸化膜を堆積して0N0 膜6 を形成した後、不純物をドープした多結晶Si膜7aを形成 する(図9(a)図示)。

【0075】(2)所定パターニングを行なったレジスト 18をマスクに、多結晶Si膜5a、0N0 膜6 、多結晶Si膜7a を異方性エッチングして、浮遊ゲート電極5 及び制御ゲ ート電極7 を形成する(図9(b)図示)。次に、多結晶Si 膜5a,7a を選択的に除去するエッチングガスを用いて、 例えばCF4 と 02 の混合ガスを用いて等方性エッチング を行なう(図9(c)図示)。

【0076】(3) レジスト18を 02 プラズマ処理と硫酸 と過酸化水素の混合液で除去し、酸素雰囲気で熱処理し 後酸化膜8 を形成した後、制御ゲート電極7 を覆うレジ スト18をマスクに不純物を注入してソース領域2 及びド レイン領域3 を形成し、レジスト18を除去する(図9(d) 図示)。この後、図示せぬが、層間絶縁膜を形成し平坦 化のため熱処理を行なった後、コンタクトホールの開 孔、配線を形成することにより、不揮発性半導体装置が 形成される。

【0077】(2)の等方性エッチング、(3)の後酸化膜 の形成時の熱処理、若しくは、(2)の等方性エッチン グ、(3)の後酸化膜の形成時、及び層間絶縁膜の平坦化 のための熱処理により、ソース領域2 側及びドレイン領 域3 側の浮遊ゲート電極5 のトンネル絶縁膜4 と接する 角の曲率半径を50nmに加工することができる。

【0078】これによれば、第一の実施例と同じくソー ス領域2 側の浮遊ゲート電極5 の角に高い電界がかから ず、さらにドレイン領域3 側の角に高い電界がかからな いため、書き込み時・読み出し時の誤書き込みを防止で きる。

【0079】また、上記理由に加え、本実施例は、複数 のメモリセルにおけるカップリング比のばらつきが第一 の実施例よりさらに減少するため、浮遊ゲート電極7 に おける電子の量を高度に制御できる。

【0080】よって本実施例によれば、信頼性の高い記 憶状態を長時間保持することができる。

【0081】尚、第一の実施例及び第二の実施例におい て、0N0 膜6 は、浮遊ゲート電極5と制御電極7 間の容 量を大きくし、制御ゲート電極7 の電位が浮遊ゲート電 極の電位に伴い変化し易くするため好ましいが、絶縁膜 であれば良くその種類及び層の数は問わない。但しSi窒 化膜は電子をトラップする性質をもつため、浮遊ゲート 電極5 または制御ゲート電極7 と直に接する膜は、Si窒 化膜以外が良い。

【0082】また、ソース領域2及びドレイン領域3を 形成するためイオン注入する不純物は、P又はAsなどN 型不純物であれば良い。

[0083]

【発明の効果】本発明は、上述のように構成されている ので、記憶情報の信頼性を向上させた記憶保持特性の高 い不揮発性半導体記憶装置をえることができる。

【図面の簡単な説明】

【図1】(a)及び(b)は、各々本発明の第一の実施例の 不揮発性半導体記憶装置を示す概略断面図、その一部分 の拡大図である。

【図2】(a) 乃至(d) は、本発明の第一の実施例の不揮 発性半導体記憶装置の製造工程を示す断面図である。

【図3】浮遊ゲート電極から電子を受ける不純物領域 浮遊ゲート電極間の電界と、電子を放出する浮遊ゲート 電極の角の曲率半径との関係を表した図である。

【図4】(a) 及び(b) は、各々NOR 型のEEPROMにおける 書き込み・読みし時のメモリセルアレイを示す概略図で ある。

【図5】NチャネルMOSFETのソース・ドレイン間の電流 値とゲート電圧の関係を表した図である。

【図 6】インテリジェント・イレーズ方式のフローチャ ートである。

【図7】消去を行なった後の、ワード線からみたしきい 値とそのしきい値を有する本実施例のメモリセル数の関 係を示す図である。

【図8】(a)及び(b)は、各々本発明の第一の実施例の 応用例にかかる不揮発性半導体記憶装置を示す概略断面 図、その一部分の拡大図である。

【図9】(a) 乃至(d) は、本発明の第一の実施例の応用 例にかかる不揮発性半導体記憶装置の製造工程を示す断

面図である。

【図10】フラッシュメモリの一般的な構成を示す概略 平面図である。

【図11】図10に示されたメモリセルアレイの概略構成 を示す等価回路図である。

【図12】(a) 及び(b) は、各々従来のフラッシュメモ リに含まれる不揮発性半導体記憶装置の平面図、(a) の a -b 線に沿ってみた断面図である。

【図13】(a) 乃至(c) は、従来の不揮発性半導体記憶 装置の製造工程を示す断面図である。

【図14】消去を行なった後の、ワード線からみたしき い値とそのしきい値を有する従来例のメモリセル数の関 係を示す図である。

| 1              | 至似      |

|----------------|---------|

| 2              | ソース領域   |

| 3              | ドレイン領域  |

| 4              | トンネル絶縁膜 |

| 4a             | Si酸化膜   |

| 5              | 浮遊ゲート電極 |

| 5a, 7a         | 多結晶Si膜  |

| 6              | 0N0 膜   |

| 7              | 制御ゲート電極 |

| <sup>-</sup> 8 | 後酸化膜    |

| 9              | チャネル領域  |

| 10             | メモリセル   |

| 11             | ビット線    |

| 12             | ワード線    |

| 13             | センスアンプ  |

| 14             | 入出力バッファ |

| 15             | 電子注入    |

| 16             | 電子の引き抜き |

| 17             | 選択メモリセル |

選択メモリセル レジスト

18

【図7】

(8)

【図11】

特開平9-17890

(9)

【図6】

【図8】

**(B)**

【図 9】

(c)

(d)

【図10】

【図12】

【図14】

【図13】

. (b)

(c )

【手続補正書】 【提出日】平成7年7月25日 【手続補正1】 【補正対象書類名】図面 【補正対象項目名】図1 (11)

【補正方法】変更 【補正内容】 【図1】

【手続補正2】 【補正対象書類名】図面 【補正対象項目名】図8

【図8】